### A Probing-Based Hardware Leakage Detection Tool

Nicolai Müller<sup>1</sup> and Amir Moradi<sup>2</sup>

<sup>1</sup> Ruhr University Bochum, Horst Görtz Institute for IT Security, Bochum, Germany firstname.lastname@rub.de

Abstract. Even today, Side-Channel Analysis attacks pose a serious threat to the security of cryptographic implementations fabricated with low-power and nanoscale feature technologies. Fortunately, the masking countermeasures offer reliable protection against such attacks based on simple security assumptions. However, the practical application of masking to a cryptographic algorithm is not trivial, and the designer may overlook possible security flaws, especially when masking a complex circuit. Moreover, abstract models like probing security allow formal verification tools to evaluate masked implementations. However, this is computationally too expensive when dealing with circuits that are not based on composable gadgets. Unfortunately, using composable gadgets comes at some area overhead. As a result, such tools can only evaluate subcircuits, not their compositions, which can become the Achilles' heel of such masked implementations.

In this work, we apply logic simulations to evaluate the security of masked implementations which are not necessarily based on composable gadgets. We developed PROLEAD, an automated tool analyzing the statistical independence of simulated intermediates probed by a robust probing adversary. Compared to the state of the art, our approach (1) does not require any power model as only the state of a gate-level netlist is simulated, (2) can handle masked full cipher implementations, and (3) can detect flaws related to the combined occurrence of glitches and transitions as well as higher-order multivariate leakages. With PROLEAD, we can evaluate masked implementations that are too complex for existing formal verification tools while being in line with the robust probing model. Through PROLEAD, we have detected security flaws in several publicly-available masked implementations, which have been claimed to be robust probing secure.

Keywords: Side-Channel Analysis · Leakage Detection · Hardware

## 1 Introduction

Since Kocher et al. reported the first Side-Channel Analysis (SCA) attacks as a threat to the security of cryptographic hardware [Koc96, KJJ99], protecting concrete implementations of cryptographic algorithms has been attracting the researchers' attention. Based on this groundbreaking work, the past twenty years of research have shown successful SCA attacks [KJJ99, BCO04, GBTP08] based on traces obtained by measuring one out of potentially various physical characteristics of a device [Koc96, KJJ99, GMO01, HS13, GST14]. In particular, if a designer does not consider SCA as a serious attack vector, an adversary may exploit the dependency between a physical characteristic of the device and the processed data revealing sensitive information efficiently.

As there has been an urgent need to mitigate information leakage, numerous countermeasures trying to protect cryptographic devices from any SCA have been proposed during

<sup>&</sup>lt;sup>2</sup> University of Cologne, Institute for Computer Science, Cologne, Germany firstname.lastname@uni-koeln.de

the past decades. So far, masking, based on the concept of secret sharing [Sha79], is the most popular proposal [CJRR99]. Masking reaches its popularity due to its basic security assumptions simplifying the design and verification of concrete masking schemes such as the ones given in [ISW03, Tri03, NRS11, RBN+15, GMK16, GMK17, GIB18, GM18]. If the masking scheme satisfies that all input sharings are drawn uniformly and if the noise level is sufficient, conceptual simple adversary models abstract the SCA security of a masking scheme [DDF14]. A basic and efficient – and therefore widely used – adversary model is the d-probing model [ISW03]. Due to its simplicity, the verification under the d-probing model is efficient but does not cover physical shortcomings. Consequently, the more advanced robust probing model has been built on top of the d-probing model to cover different types of physical defaults [FGMDP+18] including glitches, transitions, and couplings.

However, designing, implementing, and verifying a masked implementation of a cryptographic algorithm is often a manual and error-prone task. Consequently, some masking schemes are shown to be insecure because of, so far, unnoticed design flaws or inaccurate formal modeling of the adversary [MMSS19].

A common approach to verify the experimental security of a masked implementation is to collect power/electro-magnetic traces from a prototype and perform a leakage assessment based on statistical hypothesis testing, i.e. t-test [GJJR11] or  $\chi^2$ -test [MRSS18]. Leakage assessment takes place after fabricating a prototype of the device. If the leakage assessment reports a leakage, the design needs to be analyzed to avoid the flaw leading to the fabrication of a new device under test. This procedure is repeated until no further leakage is detected.

The fabrication can be a new design configured on an FPGA with a significantly short time to market. However, in the case of ASIC design procedures, refabrication is time-consuming and expensive; hence leakage evaluation techniques at early design stages, i.e., before fabrication of the chip, are getting more and more popular. In particular, formal verification and leakage simulation have become promising research fields. Nevertheless, their concrete instantiations, given as automated verification frameworks, come with restrictions. Formal verification tools can efficiently verify the robust probing security of a tiny circuit, e.g., a small S-Box, but the complete formal verification of a larger design, like a masked round-based implementation of a cipher, becomes computationally infeasible. While leakage simulation tools can handle larger circuits, they mainly check resistance against a particular Differential Power Analysis (DPA) or Correlation Power Analysis (CPA) attack, where assumptions about the leakage and power models as well as targeted intermediate values are required [HSZ13, FGBR20, NPH<sup>+</sup>20, ZPTF21]. More formally, they cannot evaluate the given circuits based on the robust probing model. As a shortcoming, they may report an implementation as secure, while an undetected design flaw (caused by not being probing secure) is exploitable by another attack not covered by the evaluations.

To build provably-secure masked implementations of large designs, small and securely composable masked circuits, so-called gadgets, are applied as building blocks of larger circuits. Therefore, the security properties of such gadgets can be individually verified by formal verification tools, e.g., [BBC+19, KSM20]. However, formal verification of a masked full cipher is still not feasible if the implementation is made by not-necessarily composable gadgets. These implementations are potentially beneficial and usually more efficient compared to their gadget-based variants. For example, [KMMS22] provides a comparison of different masked byte-serial implementations of the Advanced Encryption Standard (AES). However, their probing security remains unproven. We must rely on experimental leakage assessments that might be inaccurate, incomplete, setup-dependent, and therefore not always trustworthy. In short, we can evaluate the leakage of large designs in an experimental setting, but we cannot see this as a security proof. Even if we detect no weaknesses by a leakage assessment, we can never be sure that no security flaw exists.

#### 1.1 PROLEAD

We introduce PROLEAD, a novel leakage detection tool for hardware. PROLEAD performs logic simulations at gate level to evaluate the d-probing security of a circuit even in presence of glitches and transitions. To clarify the benefits and limitations of PROLEAD compared to the existing tools from literature, we give a detailed comparison.

**Compare with Formal Verification Tools.** All formal verification tools presented in Section 3 are restricted to the verification of small building blocks, e.g., gadgets or small S-Boxes. Hence, it is infeasible to verify large circuits, e.g., a masked implementation of a complete cipher, with formal verification tools. Due to its underlying simulation-based approach, PROLEAD can evaluate large circuits even at higher security orders. For example, a masked first-order round-based implementation of AES can be fully examined in an hour, while a flawed variant is identified in a couple of seconds. In Section 5, we evaluate some examples with PROLEAD that cannot be verified by the tools from Section 3. As a result, by means of PROLEAD we have identified a high number of security flaws in the implementations which are supposed to be not only secure in practice, but also robust probing secure. However, the evaluation of PROLEAD can be seen as incomplete, since the simulations cannot cover all possible inputs of large circuits. Therefore, it is possible that PROLEAD fails to detect existing leakage if a leaking test vector is not considered sufficiently by the simulator. Hence, increasing the number of simulations decreases the probability that existing leakage is not detected. To create confidence in the decision of PROLEAD, we provide a mechanism to determine an adequate number of simulations to consider. More specifically, we compute the minimum number of simulations needed to guarantee an acceptable small probability that existing leakage is not detected.

Compare with Leakage Simulators. The leakage simulators and evaluation techniques covered in Section 3 can give a preliminary overview of the vulnerability of the given design, often unprotected, i.e., not masked. However, they are not in conformity with the probing security model. As a result, they probably fail to detect leakage, particularly for masked implementations. In other words, they cannot guarantee the detection of leakages in flawed masked implementations. However, PROLEAD has two important differences compared to state-or-the-art leakage simulators.

- 1. PROLEAD operates directly on the simulated intermediates instead of modeling power traces. Consequently, the security evaluation does not depend on a hypothetical power model.

- 2. The evaluation procedure of PROLEAD is fully in line with the concept of robust probing security [FGMDP+18]. We investigate all necessary robust-probing adversaries that give PROLEAD the ability to detect any leakage according to the security model.

In short, PROLEAD fills the gap, i.e., uses the benefits of simulation-based tools (fast evaluations) and examines the security of large circuits based on robust probing models, which neither state-of-the-art simulation-based nor formal verification tools can handle. The tool is publicly available at  $GitHub^1$ .

#### 1.2 Outline

Section 2 starts by introducing the basic concept of probing security and continues with more advanced security notions. Afterwards, Section 2 gives the relevant background on masking and the statistical hypothesis test. Next, we present the existing tools from the

<sup>1</sup>https://github.com/ChairImpSec/PROLEAD

formal verification and leakage simulation domain in Section 3. In Section 4, we explain the methodology of PROLEAD with a focus on generating the probing sets and evaluation. Finally, we apply PROLEAD to a wide range of protected hardware implementations and discuss its findings in Section 5. Section 6 concludes this paper.

# 2 Background

### 2.1 Robust Probing Model

The robust d-probing model [FGMDP+18] extends the d-probing model [ISW03] by considering physical defaults violating security in non-ideal circuits, i.e., physical logic circuits and hardware implementations [BDF<sup>+</sup>17]. More precisely, under robust d-probing model information leakage sourced by combinational recombinations (glitches) [MPG05, MPO05], memory recombinations (transitions) [CGP+12, BGG+14], and routing recombinations (couplings) [CBG<sup>+</sup>17] are taken into account. We apply the notation from [FGMDP<sup>+</sup>18], annotating the robust probing model with a triple (g, t, c). Each entry in the triple specifies whether glitches (g=1), transitions (t=1), or couplings (c=1) are considered. For example, the (0,0,0)-robust probing model, i.e., without considering any physical defaults, is equivalent to the d-probing model introduced in [ISW03] building the theoretical foundation for verifying the security of an ideal circuit. It defines a d-probing adversary who can place up to d (standard) probes on freely chosen spots to record noise-free and stable signals. Hence, the adversary gets access to a set of d intermediates. To cover a desired physical default in the (q,t,c)-robust d-probing model, a probe extension procedure is applied on the standard probes which further increases the set of intermediates. We remark that taking all possible occurrences of a specified type of physical default into account is very conservative but leads to a model that fits arbitrary circuits.

**Glitch-Extension.** Glitches are unexpected signal transitions occurring in combinational circuits. Due to imbalanced delay paths and switching delays, signals may arrive asynchronously at a gate resulting in a different but temporary output before the output signal reaches its intended state. To cover glitches within the robust probing model, glitch-extended probes replace all probes allowing an adversary to access all stable intermediates (either register outputs or primary inputs) that contribute to the probed wire.

**Transition-Extension.** Transitions potentially recombine the contents of the same memory element in two consecutive invocations. Hence, by overwriting a memory element, i.e., a register or a flip-flop, an adversary gains information about the old and the new values. To model transitions in the robust probing model, all probes are replaced by transition-extended probes recording the signal during two consecutive invocations.

**Coupling-Extension.** Couplings lead to unintentional and undesired recombinations of values on adjacent wires. To model couplings in the robust probing model, we need to replace all probes with coupling-extended probes that observe multiple neighboring wires.

#### 2.2 Security Notions

According to the probing model, a circuit achieves (g,t,c)-robust d-probing security if a d-probing adversary cannot learn anything about the processed secret. More formally, the joint distribution of any observation set is statistically independent of the distribution of any secret. Unfortunately, for the verification of d-probing security, the statistical independence of each observation set must be checked. As the number of probe combinations grows with d and the complexity of the circuit, verification of d-probing security becomes

infeasible for large circuits and particularly at higher orders. To bypass the verification of d-probing security, small and secure building blocks, so-called gadgets, are composed to construct more complex circuits. Hence, the d-probing security of a large circuit is satisfied if all involved gadgets are composable without violating d-probing security. To formally verify the composability of a gadget, Barthe et al. introduced d-Strong Non-Interference (SNI) [BBD<sup>+</sup>16] as an extension of d-Non-Interference (NI) [BBD<sup>+</sup>15]. While gadgets satisfying d-SNI are indeed composable, it turned out that d-SNI is an over-conservative security notion in practice and leads to significant area and randomness overheads [CS20]. To relax the requirements in terms of area and randomness, Cassiers et al. introduced d-Probe-Isolating Non-Interference (PINI) as a less conservative and, therefore, more efficient security notion [CS20].

### 2.3 Boolean Masking

Boolean masking is a common and well-studied approach to protect hardware implementations against SCA attacks [CJRR99]. According to the concept of secret sharing [Sha79], Boolean masking splits a sensitive variable  $X \in \mathbb{F}_2^n$  into s > 1 independently and uniformly distributed shares  $\{X^0,...,X^{s-1}\} \in (\mathbb{F}_2^n)^s$  that satisfy  $X = \bigoplus_{i=0}^{s-1} X^i$ . To generate a sharing of X, we sample  $\{X^0,...,X^{s-2}\}$  uniformly and randomly from  $\mathbb{F}_2^n$ . For the remaining  $X^{s-1}$ , it holds that  $X^{s-1} = \left(\bigoplus_{i=0}^{s-2} X^i\right) \oplus X$ . To avoid SCA leakages about X, all operations of the cipher need to be performed on  $\{X^0,...,X^{s-1}\}$ , i.e. the shared representation of X. To achieve security under the d-probing model (cf. Section 2.1) it must hold that  $s \geq d+1$ .

# 2.4 Statistical Hypothesis Tests

Hypothesis tests apply statistical procedures to data to assess the strength of evidence against the underlying *null hypothesis*  $H_0$ . Usually,  $H_0$  denotes a general statement that there is no relation between two groups of samples. To accept or reject  $H_0$ , hypothesis tests provide a quantitative value in the form of a significance level.

For our purposes, we evaluate whether there is a significant dependency between two categorical variables R with r different categories and C with c different categories, both from a single population. Hence, the corresponding  $H_0$  states that R and C are statistically independent. The frequency of observed samples of R and C are stored in a two-way contingency table with r and c categories. For better understanding, we depict a generic two-way contingency table in Table 1.

**Table 1:** Contingency table for two variables R and C, with  $F_{i,j}$  denoting the frequency of observed samples when R = i and C = j.

| $F_{i,j}$ | j=0         | <br>j = c - 1     | Total       |

|-----------|-------------|-------------------|-------------|

| i=0       | $F_{0,0}$   | <br>$F_{0,c-1}$   | $F_{0,*}$   |

|           |             | <br>              |             |

| i = r - 1 | $F_{r-1,0}$ | <br>$F_{r-1,c-1}$ | $F_{r-1,*}$ |

| Total     | $F_{*.0}$   | <br>$F_{*,c-1}$   | $F_{*,*}$   |

**Pearson's**  $\chi^2$ -**Test of Independence.** The  $\chi^2$ -test of independence [Pea92] rejects or accepts  $H_0$  based on a test statistic that follows a  $\chi^2$ -distribution. The test itself measures the divergence of the observation from the expectation. Such expectations are done by estimating the degree of freedom v and the corresponding expected frequency  $E_{i,j}$  for

each observed frequency  $F_{i,j}$ , given that  $H_0$  holds. Afterwards, the  $\chi^2$ -test statistic x is computed as follows.

$$v = (r-1)(c-1),$$

$E_{i,j} = \frac{F_{i,*} \cdot F_{*,j}}{F_{*,*}},$   $x = \sum_{i=0}^{r-1} \sum_{j=0}^{c-1} \frac{(F_{i,j} - E_{i,j})^2}{E_{i,j}}$  (1)

The associated p-value, i.e., the probability to accept  $H_0$ , is finally computed based on the probability density function f and the gamma function  $\Gamma$ .

$$p = \int_{x}^{\infty} f(x, v) dx, \qquad f(x, v) = \begin{cases} \frac{x^{\frac{v}{2} - 1} e^{-\frac{x}{2}}}{2^{\frac{v}{2}} \Gamma(\frac{v}{2})} & x > 0\\ 0 & \text{else} \end{cases}$$

(2)

G-Test of Independence. The G-test of independence [Sok95, MoD09] is an alternative to the  $\chi^2$ -test of independence based on a likelihood ratio test. The method uses the multinomial distribution. It tests the goodness of fit of the observed to the expected frequencies, under the assumption that  $H_0$  holds, by estimating the G-statistic x as follows.

$$x = 2 \cdot \sum_{i=0}^{r-1} \sum_{j=0}^{c-1} F_{i,j} \cdot \ln\left(\frac{F_{i,j}}{E_{i,j}}\right),\tag{3}$$

where the expected frequencies  $E_{i,j}$  are computed as for the  $\chi^2$ -test, i.e., Equation (1). Since the distribution of x is approximately  $\chi^2$ -distributed with the same v, the p-value is computed in the same way as for the  $\chi^2$ -test, i.e., Equation (2).

### 2.4.1 Hypothesis Testing for Leakage Detection

Due to its simplicity and efficiency, the  $\chi^2$ -test is more common than the G-test. If the contingency table is small, i.e.  $2\times 2$ , the  $\chi^2$ -test can be easily calculated by hand. Moreover, the  $\chi^2$ -test computes a squaring while the G-test conducts the more complex logarithm function. In the field of leakage detection, the  $\chi^2$ -test is a complement to Welch's t-test as it detects some flaws which the t-test cannot detect. For a detailed comparison of the  $\chi^2$ -test and t-test, we refer to [MRSS18]. However, as the  $\chi^2$ -test is an approximation of the G-test based on Taylor expansion, it is not as accurate as of the G-test. If  $F_{i,j}$  and  $E_{i,j}$  are different, the  $\chi^2$ -test approximation overestimates the outlier what may lead to erroneous results while the G-test computes correctly [Sok95, Hoe12]. We remark that these inaccuracies occur if we deal with a sparse contingency table, i.e., the amount of data is low while the contingency table is large. As in the domain of SCA, contingency tables might often be sparse, we choose the G-test as the underlying hypothesis test of our tool PROLEAD.

For the sake of completeness, we would like to note that – in contrast to the G-test – exact hypothesis tests such as Fischer's exact test [Fis22, Agr92] do not approximate the p-value. Hence, they provide an accurate significance level. Exact tests are of great relevance when dealing with small data sets as the approximation error when applying the  $\chi^2$ -test increases the more expected frequencies are smaller than 5 [Yat34].

On the other hand, evaluating larger contingency tables with an exact hypothesis test is not feasible. Usually, Fischer's exact test is applied on up to  $2 \times 4$  contingency tables or combined with a probabilistic heuristic such as Monte Carlo sampling [M<sup>+</sup>87].

#### 2.4.2 Statistical Power Analysis

Whenever we apply statistical hypothesis tests, we ensure that we can trust their results. In particular, our experiment must satisfy that the underlying hypothesis test detects even a

small dependency. The question of whether a hypothesis test reliably detects a dependency is closely related to the metric of *statistical power*. To understand the statistical power, we first define the *estimation errors* that can occur while performing hypothesis tests in the context of SCA.

**Definition 1** (False Positive). False positives occur if we reject  $H_0$  despite it being true. It means that PROLEAD wrongly classifies a secure design as insecure.

**Definition 2** (False Negative). False negatives occur if we accept  $H_0$  despite it being false. It means PROLEAD cannot detect existing leakage and wrongly classifies an insecure design as secure.

While the p-value gives the probability of a false positive, the statistical power is related to the false-negative probability  $\beta$ . As the power of a test defines the probability that it rejects  $H_0$  correctly, it is computed as:

$$1 - \beta = F(x_{\text{crit}}, v, \lambda) = e^{\frac{-\lambda}{2}} \sum_{i=0}^{\infty} \frac{\left(\frac{\lambda}{2}\right)^i}{i!} Q(x_{\text{crit}}, v + 2i) \qquad Q(x, v) = \frac{\gamma\left(\frac{v}{2}, \frac{x}{2}\right)}{\Gamma\left(\frac{v}{2}\right)}$$

While F denotes the cumulative distribution function for the noncentral  $\chi^2$ -distribution, Q denotes the cumulative distribution function of the central  $\chi^2$ -distribution, and  $\gamma$  denotes the lower incomplete gamma function. Moreover,  $x_{\rm crit}$  defines the critical value of the underlying distribution for a given confidence level a. Hence,  $x_{\rm crit}$  estimates the a-quantile of the  $\chi^2$ -distribution. Last,  $\lambda$  is the noncentrality parameter depending on  $\varphi$  and  $F_{*,*}$  (given in Table 1) and is computed as:

$$\lambda = \varphi^2 \cdot F_{*,*}$$

As we want to detect even small effects, we choose  $\varphi=0.1$  following the proposal of Cohen [Coh88] which estimates  $\varphi=0.1$  as a small effect,  $\varphi=0.3$  as medium effect, and  $\varphi=0.5$  as huge effect. Consequently, we numerically estimate  $F_{*,*}$  for fixed  $\varphi=0.1$  and  $\beta \leq 10^{-5}$ .

### 3 Related Works

The evaluation of masked implementations has a pivotal role in protecting devices against SCA attacks. Therefore, many researchers contribute to this topic by presenting automated tools revealing flaws in protected implementations. So far, the research concentrates on two different approaches, namely formal verification, and leakage simulation.

Formal Verification. Automated tools for formal verification can prove the security of masked implementations, assisted by predefined adversary models. As formal verification is complete, no false negatives occur and the result can be seen as security proof under the chosen model but, sometimes, the verification is too conservative leading to false positives [PMK+11, KSM20]. The reduction of masking's security properties to simple and abstract adversary models allows the evaluation of complex circuits, i.e., masked implementations operating on many shares. Nevertheless, the verification under more sophisticated adversary models, i.e., models that cover physical defaults, is too computational complex for larger circuits. That is why formal verification tools are mostly applied only to gadgets. Today, a wide range of formal verification tools, evaluating robust probing security, is available [BBD+15, BBD+16, BBC+19, Cor18, BGI+18, KSM20, MKSM22, BK21, BMRT22] and we refer to [CGF21] for an exhaustive survey on formal verification tools. Below, we summarize the most relevant candidates related to this work including their capabilities. At EUROCRYPT 2015, Barthe et al. [BBD+15] presented maskVerif, a language-based

formal verification framework based on probabilistic information flow to prove the (0,0,0)and (0,1,0)-robust d-probing security of masked implementations. Moreover, they introduced the d-NI security notion and integrated an automated verification procedure into maskVerif. Later, the authors of [BBD+16] extended d-NI to the d-SNI security notion to evaluate circuits with respect to their composability, and integrated the formal verification of d-SNI into maskVerif. The introduction of the SNI notion improves formal verification since small parts of the circuit (so-called gadgets) that fulfill d-SNI can be arbitrarily composed to construct larger and still secure designs. Hence, maskVerif can efficiently verify small gadgets to avoid the formal verification of larger gadget-based circuits. As these versions of maskVerif left glitches unconsidered, Bloem et al. developed Rebecca [BGI+18], an automated tool based on the approximated estimation of Fourier coefficients. As the Fourier coefficients are not fully computed for all underlying functions of the circuit but only approximated, the precision of Rebecca might be slightly low, resulting in a small number of false positives. In contrast to maskVerif, Rebecca can verify (0,0,0)-, (1,0,0)-, and (0,1,0)-robust d-probing security but no composability notions as d-NI and d-SNI are supported. Nevertheless, the computational cost for estimating Fourier coefficients is quite high which restricts Rebecca to the verification of small circuits and low security orders. Moreover, Barthe et al. extended maskVerif to evaluate higher-order leakages in the presence of glitches [BBC<sup>+</sup>19]. The extension is based on a simple but expressive intermediate language that annotates each instruction with a leakage expression. Since the to-date version of maskVerif can verify large sets of intermediates very efficiently, the performance is improved compared to former versions [BGI<sup>+</sup>18]. However, maskVerif follows a language-based approach resulting in verification purely based on the syntax instead of statistical evaluation. Therefore, a false positive can occur if a statistical independent output of a masked function violates non-completeness and its sharing is not refreshed by fresh randomness. Two examples for such a false classification are the Threshold Implementation (TI) of PRESENT S-Box given in [PMK+11] which maskVerif wrongly classifies as first-order insecure, and a small toy example presented in [KSM20]. In short, neither Rebecca nor maskVerif can fully avoid false positives. To counteract this problem, Knichel et al. presented SILVER [KSM20], which completely avoids false positives by analyzing the statistical independence of joint distributions. Moreover, SILVER supports all previously discussed security notions (d-probing security, d-NI, and d-SNI) as well as the d-PINI notion [CS20], which allows composability as well as a more efficient implementation compared to d-SNI. All security notions can be verified under the (0,0,0)and (1,0,0)-robust d-probing model, i.e., covering glitches. Concerning efficiency, SILVER achieves fast verification of gadgets at higher orders as well as small S-Boxes on low orders. On the negative side, SILVER is not able to analyze even a middle-size masked circuit. By a recent extension [MKSM22], SILVER is also able to evaluate a certain form of circuits under the (1,1,0)-robust d-probing model. Hence, SILVER was the first formal verification tool that covers glitches and transitions simultaneously. While the current versions of maskVerif and SILVER can verify a design under various conditions, the overhead in terms of verification time, especially for verification with SILVER is impractical for large circuits.

**Leakage Simulation.** Since the formal verification of larger circuits becomes infeasible, another research branch focuses on evaluating these circuits by simulating the power consumption of a particular prototype running the implementation. For efficiency reasons, only a fixed set of input vectors is simulated resulting in an incomplete evaluation. Hence, the high performance of leakage simulation comes at the cost of accuracy and false negatives. We remark that [BBYS22] presents a wide range of leakage simulators. Therefore, we focus on how simulators abstract the leakage. The accuracy of a simulator mainly depends on the abstraction level of the simulation. Simulations at the Register-Transfer Level (RTL) are helpful to verify the security of a hardware implementation during the earliest design

stage. Since a high-level description is the only available source, the simulation cannot take any hardware-specific internals into account. Usually, the simulation of a trace on RTL is done by simulating the internal logic given in the high-level description and applying a leakage function like Hamming weight (HW) [AMM<sup>+</sup>06, Rep16, FGBR20] or Hamming distance (HD) [SBY<sup>+</sup>18] on the logically simulated intermediates. Then, conventional leakage assessment techniques as Test Vector Leakage Assessment (TVLA) [BCD<sup>+</sup>13] operate on the simulated traces. To increase accuracy, Debande et al. proposed a profiled logic simulator based on linear regression [DBBL12]. During a profiling phase, the simulator receives real traces from a profiling device and two successive states of all registers to fit a function of state bits and transitions [SLP05]. According to the resulting model, the simulator can generate new traces that are more accurate compared to non-profiled high-level simulators. Furthermore, some tools are build to identify possible hypothesis functions for an exploitation with DPA and CPA [HSZ13, HPN+19, NPH<sup>+</sup>20, ZPTF21]. If a gate-level netlist is available, simulations become more detailed and leakage can be detected for each cell separately. Nevertheless, taking every single gate into account increases the simulation time significantly. Most of the gate levelsimulators consider simulated toggles which are stored in a Value Change Dump (VCD) file [KP07, SBY<sup>+</sup>18, SVRK19, YKES20]. Based on the toggles, they simulate the traces which are again processed by TVLA. Sometimes the user can annotate the netlist. For example, the simulator of Kirschbaum et al. [KP07] can simulate glitches if the user adds propagation delays to the netlist. Furthermore, Karna splits the placed netlist into  $N \times N$  regions and identifies the most leaking ones with localized TVLA if the user adds placement information [SVRK19]. To allow a fair comparison of gate-level leakage leakage detection on a prototype, Kiaei et al. developed the Saidoyoki evaluation board [KLE<sup>+</sup>21]. The board includes two self-designed ASICs. The simulator receives a gatelevel netlist, layout parasitics, and a test scenario (DPA, CPA, or TVLA) together with a fitting set of test vectors. Then, the procedure applies commercial tools for synthesis, hardware simulation, and gate-level leakage estimation. Simulators operating at a low abstraction level, e.g. transistor level, such as Simulation Program with Integrated Circuit Emphasis (SPICE) and its variants, can simulate the power consumption very accurately as they take many hardware-specific properties into account. Therefore, transistor-level simulations achieve the highest accuracy and are widely used to model side-channel leakage [TV04, AMM+06, RBE+07, RCS+09, SBY+18]. Nevertheless, covering all design internals comes at the cost of performance [TV03]. Hence, transistor-level simulations become infeasible for large circuits [BDG<sup>+</sup>14].

# 4 Technique

The procedure PROLEAD follows to verify d-probing security consists of two steps. Initially, PROLEAD generates all probing sets that must be considered for the desired leakage verification. Later, a verification step goes through all relevant probing sets and tests their information leakage. During verification, a simulator generates the inputs for the circuit (based on the given settings) and simulates the circuit to obtain intermediate values. Afterwards, a statistical hypothesis test evaluates the independence of the intermediate's underlying distributions. In this section, we present both steps in detail. We start by reviewing the leakage models PROLEAD supports and give some information about the specification of the settings.

#### 4.1 Notation

We denote functions by sans-serif lower-case characters, e.g. f(.). We use an upper-case and bold character, like X, to denote a list of elements. Further, we use subscripts to refer

to a specific element of a list. For example,  $x_i \in \mathbf{X}$  denotes the element with index i in the list.

#### 4.2 Formal Models

#### 4.2.1 Circuit Model

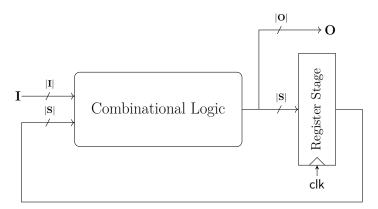

It holds that every sequential circuit that contains no combinational loop (i.e., not covering circuits with an asynchronous design architecture) can be uniquely modeled as a Mealy machine [Mea55] following the schematic of Figure 1. The circuit model combines combinational logic with a single register stage containing all synchronization elements. Hence, even if a circuit encompasses multiple register stages, it is modeled as it is depicted in Figure 1. The combinational logic processes the primary inputs I and the register state S, and returns all register inputs and primary outputs O.

**Figure 1:** General model of a sequential circuit.

**Definition 3** (Mealy Machine). We represent a *Mealy Machine* as a directed graph  $(\mathbf{V}, \mathbf{E})$ . Each vertex  $v \in \mathbf{V}$  models a combinational gate or a register cell while we model each connection between the gates, i.e., wires, as an edge  $e \in \mathbf{E}$ . Each  $v \in \mathbf{V}$  is defined as a quadruple  $v = (\mathbf{E}_v^{\text{in}}, \mathbf{E}_v^{\text{out}}, \mathsf{f}_v, g_v)$  with the following elements:

- The input wires  $\mathbf{E}_v^{\text{in}} \subseteq \mathbf{E}$  (and output wires  $\mathbf{E}_v^{\text{out}} \subseteq \mathbf{E}$ ) of v.

- The underlying Boolean function  $f_v$  computed by v.

- $g_v \in \mathbb{F}_2$  with  $g_v = \text{true}$  if v is combinational, and  $g_v = \text{false}$  if v is a sequential gate.

We remark that  $e \in \mathbf{E}$  only specifies the signal itself (i.e. the output value of a gate) but not the connection between multiple gates. Hence, a connection from  $v_0$  to  $v_1$  with  $v_0, v_1 \in \mathbf{V}$  exists if  $e \in \mathbf{E}_{v_0}^{\mathrm{out}}$  and  $e \in \mathbf{E}_{v_1}^{\mathrm{in}}$ . Further,  $e \in \mathbf{E}$  can be the input of multiple gates as the same signal can be the input of multiple gates. Additionally, we create a list  $\mathbf{V}_e \subseteq \mathbf{V}$  for each  $e \in \mathbf{E}$ .  $\mathbf{V}_e$  stores all  $v \in \mathbf{V}$  with  $e \in \mathbf{E}_v^{\mathrm{in}}$ .

#### 4.2.2 Leakage Models

To verify d-probing security, PROLEAD can be dictated to consider a specification of the (g,t,c)-robust d-probing model [FGMDP<sup>+</sup>18].

**Definition 4** (Probe). Let  $(\mathbf{V}, \mathbf{E})$  be the representation of a sequential circuit and  $\mathbf{T}$  be a list of considered time instances, i.e. clock cycles. A probe p = (e, t) with  $e \in \mathbf{E}$  and  $t \in \mathbf{T}$  records a signal on wire e during clock cycle t.

**Definition 5** (Probing Set). A Probing Set  $\mathbf{P} = \{p_0, ..., p_{|\mathbf{P}|-1}\}$  defines a list of probes. We denote the extensions applied to a probing set  $\mathbf{P}$  with superscripts. For example, if  $\mathbf{P}$  contains standard probes, we refer to the same list when extended by glitches by  $\mathbf{P}^g$ .

By default, we perform the verification step under the (1,0,0)-robust d-probing model. This so-called glitch-extended d-probing model is a widely-used adversary model for hardware implementations. It considers physical defaults in terms of glitches. To formalize the behavior of glitches, i.e., their propagation through combinational logic, we utilize the conservative glitch-extension procedure from [FGMDP<sup>+</sup>18] given in Definition 6.

**Definition 6** ((1,0,0)-Robust *d*-Probing Model). Consider a list of *d*-probing sets  $\mathbf{P}$ . We transform all *d*-probing sets  $\mathbf{P}_i = \{p_0, ..., p_{d-1}\} \in \mathbf{P}$  into glitch-extended probing sets  $\mathbf{P}_i^g \in \mathbf{P}^g$  by substituting each probe  $p \in \mathbf{P}_i$  individually. We substitute p = (e,t) by all probes placed on the input wires of combinational gates that contribute to e and record during clock cycle t.

Then, the verification step goes through all  $\mathbf{P}_i^g \in \mathbf{P}^g$  and analyzes each glitch-extended probing set. We give the details of the probe extension procedure in Section 4.4. Further, we can expand the verification by considering the joint occurrence of glitches and transitions under the (1,1,0)-robust d-probing model. Usually, hardware implementations are analyzed concerning glitches only. However, transitions can lead to security flaws, especially in iterative circuits, e.g., round-based cipher designs [HSS12, CS21]. Formalizing the influence of transitions, i.e., value changes, whose leakage depends on the previous as well as the new value, is done by extending all  $p \in \mathbf{P}^g$  by transitions according to Definition 7.

**Definition 7** ((1,1,0)-Robust *d*-Probing Model). Consider a list of glitch-extended *d*-probing sets  $\mathbf{P}^g$ . We transform all  $\mathbf{P}^g_i = \{p_0,...,p_{|\mathbf{P}^g_i|-1}\} \in \mathbf{P}^g$  into  $\mathbf{P}^{g,t}_i \in \mathbf{P}^{g,t}$  by substituting all  $p = (e,t) \in \mathbf{P}^g_i$  with a tuple  $\{p,p'\}$  recording the previous clock cycle p' = (e,t-1).

We should highlight that PROLEAD always considers the glitches and does not support non-robust (0,0,0) case. As PROLEAD is supposed to evaluate hardware circuits, we cannot ignore glitches. For a correct evaluation, the user should also consider transitions. However, we made the cover of transitions an optional feature to allow the designer to identify the source of leakage. More precisely, if PROLEAD reports the detection of leakage for glitch + transitions, the designer can turn off the transitional effect and re-evaluate the circuit to find whether the detected leakage is due to the glitches or not. Further, PROLEAD does not cover coupling as information about the layout becomes required, i.e., placement of cells and routing of signals. Since PROLEAD works with the gate-level netlist as the result of a synthesis process, such information is not available. Moreover, the user can restrict the verification of higher-order probing security to univariate leakages or cover multivariate leakages as well.

Univariate Leakage. Univariate attacks exploit leakage during a single point in time. Hence, we formalize the verification of univariate d-order probing security by an attacker who places up to d probes at the same clock cycle. Therefore, an attacker can spot up to d intermediates during a single but arbitrary clock cycle. We model the attacker's capabilities by verifying all relevant probing sets whose probes record during the same clock cycle. More formally, it holds that all probes  $p \in \mathbf{P}_i$  record during the same clock cycle.

**Multivariate Leakage.** In contrast to the univariate setting, a v-variate attack combines information of v different points in time [MM12]. Consequently, a multivariate attacker can place each probe at an arbitrary clock cycle. To formalize the adversary's behavior,

we make no restrictions on the probing sets concerning the clock cycles. Hence, a probing set can contain probes at any relevant gate and record at any clock cycle. Note that by 'any relevant gate' we refer to the list  $\mathbf{E}^*$  defined below, and by 'any clock cycle' we still stay with the targeted clock cycles (given as a list  $\mathbf{T}$ ) defined in the configuration file by the user.

### 4.3 Configuration

PROLEAD receives three input files.

- 1. A gate-level netlist written in Verilog as used in digital circuit design to abstract the circuit. Such a netlist is produced by synthesizing the circuit's behavioral description (e.g., VHDL or Verilog) using a hardware synthesizer, e.g., Design Compiler [Inc] or Yosys [Wol].

- 2. Any ASIC standard cell library can be used for the synthesis, but the functional behavior of each cell of the library should be defined in a custom file, which should be given to PROLEAD as well. Such a file is required for the simulator of PROLEAD to understand how to simulate the cells used in the given netlist. We integrated the functional behavior of most of the cells in NanGate 45 nm open-cell library.

- 3. A custom configuration file, allowing the users to specify their requirements. All settings regarding simulation and verification take place in this file. Primarily, the user adjusts the simulator by defining the total number of simulations and the simulation time frame in terms of clock cycles. To start a simulation, the user should ensure a correct initialization of the primary inputs to the circuit by defining an input sequence. The input sequence formalizes the state of all primary inputs during an arbitrary number of initial cycles. For example, in case of a cryptographic core, how and when plaintext and key should be given to the circuit and how handshaking signals (like reset) are controlled.

For verification, PROLEAD supports a customized list of wires, which is also defined by the user. Formally, a wire is either considered in the verification or ignored. The user specifies this by including the considered wire into the list  $\mathbf{E}^*$ . To ease the definition  $\mathbf{E}^*$  by the user, we include all wires to the list by default. Hence, the default case is to perform a complete evaluation in terms of wires. Furthermore, the user specifies the leakage verification by setting an appropriate security order d and choosing a proper leakage model. The configuration file contains more fine-grained settings which we ignore to express here for the sake of brevity.

### 4.4 Generation of Probing Sets

After reading the given design and configuration files, and making the graph  $(\mathbf{V}, \mathbf{E})$ , as the first step PROLEAD generates all d-probing sets that fit the desired leakage evaluation specified in the configuration file. Depending on the leakage model, the probing set generation specifies either  $\mathbf{P}^g$  or  $\mathbf{P}^{g,t}$ . Both lists encompass all probing sets (either  $\mathbf{P}^g$  or  $\mathbf{P}^{g,t}$ ) that are considered for verification. In the following, we algorithmically describe all steps required to generate the probing sets.

#### 4.4.1 Extraction of Relevant Wires

We start by determining which  $e \in \mathbf{E}$  are relevant for the verification procedure. For efficiency reasons, we generate a small list of relevant wires  $\mathbf{H}$  as long as they fit the defined configuration. The generation of  $\mathbf{H}$  is presented in Algorithm 1. As we, at least, consider glitches, every probe p gets extended by probes on the whole combinational circuit

that contributes to the intermediate signal probed by p. According to the circuit model (cf. Figure 1), a probe p on an intermediate signal of the combinational logic leads to additional probes on a subset of primary inputs and register outputs. We consider the n-bit output of the combinational circuit, with  $n = |\mathbf{S}| + |\mathbf{O}|^2$  as a set of n coordinate functions  $\left\{\mathsf{f}_0(\mathbf{I}_0,\mathbf{S}_0),...,\mathsf{f}_{n-1}(\mathbf{I}_{n-1},\mathbf{S}_{n-1})\right\}$  while each  $\mathsf{f}_j$  operates on an individual set of primary inputs  $I_j \subseteq I$  and register outputs  $S_j \subseteq S$ . For illustration, we consider the following example based on a single coordinate function  $f_i(\mathbf{I}_i, \mathbf{S}_i)$ . Since the subcircuit computing  $f_j(\mathbf{I}_j, \mathbf{S}_j)$  is fully combinational, a single probe on the output of  $f_i(\mathbf{I}_i, \mathbf{S}_i)$  expands to probes on all signals in  $I_j$  and  $S_j$ . Hence, placing additional probes on intermediate signals of a coordinate function is not necessary as all inputs of  $f_j$  are already covered. Therefore, we don't have to consider a probe on every intermediate signal of the circuit. It is enough to place probes on all output wires of the combinational circuit  $\{S \cup O\}$ . Consequently, we add the output wires of all coordinate functions to H. To this end, we need to be in conformity with the user-defined configuration regarding allowed and ignored signals. More precisely, it should hold that  $\mathbf{H} \subseteq \mathbf{E}^*$ . We satisfy these properties for each  $e \in \mathbf{H}$ by analyzing only elements in  $\mathbf{E}^*$  (cf. Line 2 of Algorithm 1). To examine if a signal is the output of a coordinate function, we determine whether the circuit propagates the underlying signal to another combinational gate. This is done in Lines 4-8. Considering the circuit model, given in Section 4.2.1, each  $e \in \mathbf{H}$  can only be either an input of the registers or a primary output which is additionally not an input of any combinational gate.

#### Algorithm 1 Extraction of relevant wires

```

Input: E*

▷ Lists of desired (included) wires

Output: H

▷ List of relevant wires

1: H ← ∅

2: for \forall e \in \mathbf{E}^* \ \mathbf{do}

▶ Analyze all considered signals of the circuit

3:

\alpha \leftarrow \mathtt{true}

4:

for \forall v \in \mathbf{V}_e do

\triangleright Analyze all cells that receive the signal e as input

if g_v = true then

▷ Check if the signal is given to a combinational gate

5:

\alpha \leftarrow \mathtt{false}

6:

end if

7:

end for

8:

if \alpha = \mathtt{true} \ \mathtt{then}

9:

\mathbf{H} = \mathbf{H} \cup \{e\}

▶ Add the considered wire to the list

10:

end if

11:

12: end for

```

#### 4.4.2 Combination of Probes

After inserting all relevant wires of the circuit into  $\mathbf{H}$ , based on the user-defined configuration we place and combine the probes resulting in multiple (yet non-extended) d-probing sets  $\mathbf{P}_i \in \mathbf{P}$ . For efficiency reasons, we avoid duplicates in all  $\mathbf{P}_i \in \mathbf{P}$ . Hence, it holds that  $p_j \neq p_k$  for all  $p_j, p_k \in \mathbf{P}_i$  with  $j \neq k$ . Furthermore, the order of probes inside the probing set does not affect the verification. We abstract the generation of all  $\mathbf{P}_i \in \mathbf{P}$  as finding all possible d-combinations of elements  $\mathbf{L}'$  with  $|\mathbf{L}'_i| = d$  and  $\mathbf{L}'_i \in \mathbf{L}'$  in a predefined list of elements  $\mathbf{L} = \{l_0, \ldots, l_{|\mathbf{L}|-1}\}$  which is a common problem in combinatorics. We show the generation of all possible d-combinations in  $\mathbf{L}'$  in Algorithm 2. For simplicity, we operate on a bit-vector of  $|\mathbf{L}|$  indices  $\mathbf{M} = \langle m_0, \ldots, m_{|\mathbf{L}|-1} \rangle$  with  $m_i \in \mathbb{F}_2$ . Initially, it holds that  $m_i = 1$  if i < d and  $m_i = 0$  otherwise to start with the first combination, i.e., Line 3 of

<sup>&</sup>lt;sup>2</sup>There might be some overlap between the signals of S and O, but this does not harm the given definitions.

Algorithm 2. In Lines 15-32,  $\mathbf{M}$  is modified to represent the next possible d-combination of element indices. Based on the current combination of indices shown by  $\mathbf{M}$ , we store the corresponding d-combination  $\mathbf{L}'_i = \{l_{m_0}, \ldots, l_{m_{d-1}}\}$  before the indices are updated (cf. Line 13). Our algorithm terminates if the last d-combination is reached. This is the case if it holds that  $m_i = 0$  for all  $i < |\mathbf{L}| - d$ . We capture the last combination in Line 6.

```

Algorithm 2 Make d-combinations of elements

\overline{\mathbf{Input:}} \ \mathbf{L} = \{l_0, \dots, l_{|\mathbf{L}|-1}\}

▶ List of elements

Input: d

▶ Size of combinations

Output: \mathbf{L}' = \{\mathbf{L}'_0, \dots, \mathbf{L}'_{\binom{|\mathbf{L}|}{d}-1}\}

\triangleright Lists of d-combinations

1: \alpha \leftarrow \mathtt{true}

2: \mathbf{M} \leftarrow \langle m_0, .., m_{|\mathbf{L}|-1} \rangle, \forall m_i = 0

\triangleright Initialize a vector that stores the element indices

3: for i \in \{0, \dots, d-1\} do

▶ Get the first combination

4:

m_i \leftarrow 1

5: end for

6: while \alpha = \text{true do}

7:

\mathbf{F} \leftarrow \emptyset

▷ Get an empty temporary probing set

for i \in \{0, ..., |\mathbf{L}| - 1\} do

8:

if m_i = 1 then

9:

\mathbf{F} \leftarrow \mathbf{F} \cup \{l_{m_i}\}

> Store the element in the combination

10:

end if

11:

12:

end for

\mathbf{L'} \leftarrow \mathbf{L'} \cup \mathbf{F}

\triangleright Add the d-combination to the list

13:

\alpha \leftarrow \mathtt{false}

14:

15:

for i \in \{0, ..., |\mathbf{L}| - 1\} do

▶ Get next combination

if m_i = 1 \wedge m_{i+1} = 0 then

16:

\alpha \leftarrow \mathtt{true}

17:

m_i \leftarrow 0

18:

m_{i+1} \leftarrow 1

19:

20:

s \leftarrow 0

for j \in \{0, ..., i-1\} do

21:

if m_j = 1 then

22:

m_i \leftarrow 0

23:

s \leftarrow s + 1

24:

end if

25:

end for

26:

for j \in \{0, ..., s-1\} do

27:

m_i \leftarrow 1

28:

end for

29:

30:

break

end if

31:

32:

end for

33: end while

```

However, to compute the probing sets, we have to specify  $\mathbf{L}$  and add the relevant timing information. As the relevant timing combinations differ for the univariate and multivariate cases, we present each procedure separately.

**Univariate Probe Generation.** Covering only univariate leakages leads to a straightforward probe generation approach shown in Algorithm 3. As all probes must be annotated with the same clock cycle, we generate *d*-combinations according to Algorithm 2 applied on

**H**. Afterwards, we consider the *d*-combinations of wires  $\mathbf{H}' = \{\mathbf{H}'_0, \dots, \mathbf{H}'_{\binom{|\mathbf{H}|}{d}-1}\}$  and the relevant clock cycles  $\mathbf{T} = \{t_0, \dots t_{|\mathbf{T}|-1}\}$ . For each  $\mathbf{H}'_i \in \mathbf{H}'$  with  $\mathbf{H}'_i = \{e'_0, \dots e'_{d-1}\}$  and each  $t \in \mathbf{T}$ , we compute a probing set  $\mathbf{P} = \{p_0, \dots, p_{d-1}\}$  with  $p_j = (e'_j, t)$ . This procedure results in  $|\mathbf{H}'| \cdot |\mathbf{T}|$  probing sets. For example, suppose that d = 2 and  $\mathbf{H}'_0 = \{e_0, e_1\}$  and three targeted clock cycles  $\mathbf{T} = \{t_0, t_1, t_2\}$ . To consider  $\{t_0, t_1, t_2\}$ , we generate  $|\mathbf{T}|$  probing sets

```

\mathbf{P}_0 = \{(e_0, t_0), (e_1, t_0)\}, \quad \mathbf{P}_1 = \{(e_0, t_1), (e_1, t_1)\}, \quad \mathbf{P}_2 = \{(e_0, t_2), (e_1, t_2)\}.

```

In other words,  $\mathbf{P}_i$  covers all probes from  $\mathbf{H}'_0$  recording at clock cycle  $t_i$ .

```

Algorithm 3 Univariate probing set generation

\overline{\mathbf{Input: H}} = \{e_0, \dots, e_{|\mathbf{H}|-1}\}

▷ List of relevant wires

Input: T = \{t_0, \dots, t_{|T|-1}\}

▷ List of relevant clock cycles

Output: \mathbf{P} = \{\mathbf{P}_0, \dots, \mathbf{P}_{\binom{|\mathbf{H}|}{d}) \cdot |\mathbf{T}|-1}\}

▶ A list of probing sets

1: \mathbf{H}' \leftarrow \text{result of Algorithm 2 on } \mathbf{H}

2: \mathbf{for} \ i \in \{0, \dots, \binom{|\mathbf{H}|}{d} - 1\} \ \mathbf{do}

3: \{e'_0, \dots, e'_{d-1}\} \leftarrow \mathbf{H}'_i

4: \mathbf{for} \ j \in \{0, \dots, |\mathbf{T}| - 1\} \ \mathbf{do}

\mathbf{R} \leftarrow \emptyset

▷ Generate a temporary empty probing set

5:

for l \in \{0, \dots, d-1\} do

6:

p \leftarrow (e'_l, t_j)

▶ Generate and place a single probe

7:

\mathbf{R} \leftarrow \mathbf{R} \cup \{p\}

▶ Add the probe to the probing set

8:

end for

9:

\mathbf{P} \leftarrow \mathbf{P} \cup \mathbf{R}

10:

end for

11:

12: end for

```

**Multivariate Probe Generation.** In this case, each probe  $p \in \mathbf{P}$  can be annotated with every targeted clock cycle  $t \in \mathbf{T}$ . Hence, each possible d-combination of  $\mathbf{T}$  is a possible annotation for  $\mathbf{P}$ . Before we apply Algorithm 2, we generate a list of considered probes  $\mathbf{P}'$  by storing probes on all relevant wires  $e \in \mathbf{H}$  and at every time instance  $t \in \mathbf{T}$ . Hence, the resulting set  $\mathbf{P}'$  encompasses  $|\mathbf{H}| \cdot |\mathbf{T}|$  probes. Afterwards, we apply Algorithm 2 on  $\mathbf{P}'$  in order to generate the d-probing sets. We again explain this by an example. Suppose d = 2 and two relevant wires  $\mathbf{H} = \{e_0, e_1\}$  and the targeted clock cycles  $\{t_0, t_1, t_2\}$ . This results in six relevant probes  $\mathbf{P}' = \{p_0, p_1, p_2, p_3, p_4, p_5\}$ . It holds that:

$$p_0 = (e_0, t_0), p_1 = (e_0, t_1), p_2 = (e_0, t_2),$$

$p_3 = (e_1, t_0), p_4 = (e_1, t_1), p_5 = (e_1, t_2)$

Applying Algorithm 2 on  $\mathbf{P}'$  returns  $\binom{|\mathbf{H}| \cdot |\mathbf{T}|}{d}$  d-probing sets:

$$\mathbf{P}_0 = \{p_0, p_1\}, \ \mathbf{P}_1 = \{p_0, p_2\}, \ \mathbf{P}_2 = \{p_1, p_2\}, \ \mathbf{P}_3 = \{p_0, p_3\}, \ \mathbf{P}_4 = \{p_1, p_3\},$$

$$\mathbf{P}_5 = \{p_2, p_3\}, \ \mathbf{P}_6 = \{p_0, p_4\}, \ \mathbf{P}_7 = \{p_1, p_4\}, \ \mathbf{P}_8 = \{p_2, p_4\}, \ \mathbf{P}_9 = \{p_3, p_4\},$$

$$\mathbf{P}_{10} = \{p_0, p_5\}, \ \mathbf{P}_{11} = \{p_1, p_5\}, \ \mathbf{P}_{12} = \{p_2, p_5\}, \ \mathbf{P}_{13} = \{p_3, p_5\}, \ \mathbf{P}_{14} = \{p_4, p_5\}$$

We show the corresponding procedure, i.e., multivariate generation of d-probing sets, in Algorithm 4. Storing all possible probes  $p \in \mathbf{P}'$  is given in Line 2-7.

```

Algorithm 4 Multivariate probing set generation

Input: \mathbf{H} = \{e_0, \dots, e_{|\mathbf{H}|-1}\}

▷ List of relevant wires

Input: T = \{t_0, \dots, t_{|T|-1}\}

▶ List of relevant clock cycles

Output: P = \{P_0, \dots, P_{\binom{|\mathbf{H}| \cdot |\mathbf{C}|}{1-1}}\}

▶ A list of probing sets

1: \mathbf{P}' \leftarrow \emptyset

▷ Get an empty list of considered probes

2: for i \in \{0, \dots, |\mathbf{H}| - 1\} do

for j \in \{0, ..., |\mathbf{C}| - 1\} do

p \leftarrow (e_i, c_j)

4:

\mathbf{P}' \leftarrow \mathbf{P}' \cup \{p\}

5:

▷ Store all considered probes

6:

end for

7: end for

8: \mathbf{P} \leftarrow \text{result of Algorithm 2 on } \mathbf{P}'

```

#### 4.4.3 Probe Extension

Up to now,  $\mathbf{P}$  contains all probing sets relevant for verification under the (0,0,0)-robust d-probing model, i.e., still non-extended. However, as we take glitches and, if specified, transitions into account, we should extend  $\mathbf{P}$ . Both supported models cover glitches; hence, we start by transforming  $\mathbf{P}$  into  $\mathbf{P}^g$  containing all glitch-extended probing sets. For the sake of efficiency, we process every  $e \in \mathbf{H}$  and precompute its set of wires after glitch-extension  $e^g \in \mathbf{H}_e^g$ . To this end, we use a recursive backpropagation procedure given in Algorithm 5. In short, for the given  $e \in \mathbf{H}$ , the procedure checks if the probe extension stops, i.e., whether e is a register output or a primary input (see Line 6). If so, e is added to  $\mathbf{H}_e^g$ . Otherwise, the same procedure is repeated for all inputs of the gate whose output is e (Lines 10-13). Having the lists  $\mathbf{H}_e^g$  for all  $e \in \mathbf{H}$ , it is enough to substitute every probe e in all e-probing sets e0 with the corresponding glitch-extended probing set. This is done by replacing e1 with e2 with e3 for all e3. This way, e4 which is equivalent to e4 under the e4, only robing model is achieved.

```

Algorithm 5 Glitch extension

\rhd \ Circuit \ graph

Input: (V, E)

Input: e \in \mathbf{H}

▶ A single signal

Output: \mathbf{H}_{e}^{g}

\triangleright The list of probed signals after glitch-extension

1: for i \in \{0, \dots, |\mathbf{V}| - 1\} do

if e \in \mathbf{E}_{v_i}^{\mathrm{out}} then

2:

3:

v \leftarrow v_i

\triangleright The cell whose output is e

end if

4:

5: end for

6: if (\mathbf{E}_v^{\text{in}} = \emptyset) \vee (g_v = \text{false}) then

\triangleright If e is a primary input or a register output

\mathbf{H}_e^g \leftarrow \{e\}

7:

else

8:

\mathbf{H}_{e}^{g} \leftarrow \emptyset

9:

for l \in \mathbf{E}_{v}^{\mathrm{in}} do

\triangleright All inputs of the gate v

10:

\mathbf{G}_{e}^{g} \leftarrow \text{result of Algorithm 5 on } (\mathbf{V}, \mathbf{E}), l

11:

\mathbf{H}_{e}^{g} \leftarrow \mathbf{H}_{e}^{g} \cup \mathbf{G}_{e}^{g}

12:

13:

end for

14: end if

```

**Extension based on Transitions.** After the generation of  $\mathbf{P}^g$  and possible optimizations (explained below), the extension for transitions is done straightforwardly. Namely, every

probe  $p=(e,c)\in \mathbf{P}_i^g\in \mathbf{P}^g$  is substituted by a tuple of two probes recording the same signal but at two consecutive clock cycles, i.e.,  $\{p,p'\}$  with p=(e,c) and p'=(e,c-1). Hence,  $\mathbf{P}^{g,t}$  is constructed.

#### 4.4.4 Optimizations

The verification step can evaluate the list of probing sets  $\mathbf{P}^g$  or  $\mathbf{P}^{g,t}$  to verify d-probing security. However, avoiding unnecessary probes and probing sets accelerates the verification procedure. In particular, we remove probes and probing sets if they fulfill one of the properties defined below.

**Definition 8** (Duplicate). Consider a probing set **P** and two probes  $p_i, p_j \in \mathbf{P}$ . We refer to the tuple  $(p_i, p_j)$  as a *duplicate* if  $p_i = p_j$  and  $i \neq j$ . Hence, **P** contains the same probe twice.

**Definition 9** (Subsequence). Consider two probing sets P, R. We refer to P as a subsequence of R if  $P \subseteq R$ . Hence, P is fully covered by R.

Due to the construction of  $\mathbf{P}$  (cf. Algorithm 3 and Algorithm 4) neither duplicates nor subsequences can occur in the set of standard probes. However, duplicates, as well as subsequences, are introduced during the glitch extension. In particular, if multiple but different probes lead to overlapping probing sets after glitch extension. Therefore, we remove duplicates and subsequences after the glitch extension. As the transition extension is a bijection (two different probes never share the same transition-extended probe), extending  $P^g$  with transitions does not introduce new duplicates or subsequences.

Removing Duplicated Probes. We remark that detecting duplicates in a sorted probing set  $\mathbf{P}_i^g$  has a complexity of  $\mathcal{O}(|\mathbf{P}_i^g|)$ . Therefore, we sort each duplicate-prone probing set  $\mathbf{P}_i^g \in \mathbf{P}^g$  with IntroSort [Mus97]. As IntroSort has a complexity of  $\mathcal{O}(|\mathbf{P}_i^g|\log|\mathbf{P}_i^g|)$  the sorting is very fast.

Removing Subsequences. First, we remove duplicated probing sets  $\mathbf{P}_i^g \in \mathbf{P}^g$  with  $\mathbf{P}_i^g = \mathbf{P}_{j \neq i}^g$  which are easy to identify. To this end, we apply IntroSort to sort the probing sets of  $\mathbf{P}^g$ . Afterwards, we go through all probing sets in  $\mathbf{P}^g$  and remove every  $\mathbf{P}_i^g \in \mathbf{P}^g$  with  $\mathbf{P}_i^g = \mathbf{P}_{i-1}^g$ . It means that we remove all duplicates of  $\mathbf{P}_i^g$  except its first occurrence. Second, we search for all tuples  $(\mathbf{P}_i^g, \mathbf{P}_{j \neq i}^g)$  with  $\mathbf{P}_i^g \subset \mathbf{P}_j^g$ . If a tuple is found, we mark  $\mathbf{P}_i^g$  as a probing set to be removed and ignore it in further searches. Finally, all marked probing sets are removed from  $\mathbf{P}^g$ . As the search for tuples has the complexity of  $\mathcal{O}(n^2)$ , we can increase the efficiency through parallelization. Each thread can compare a dedicated set of probing sets  $\mathbf{P}_i^g \in \mathbf{P}^g$  with all other probing sets in  $\mathbf{P}^g$  and mark  $\mathbf{P}_i^g$  in a shared memory if  $\mathbf{P}_i^g$  should be removed. After the termination of all threads, the entire marked probing sets can be removed. Since this process may take a very long time if the circuit is very large and a high security order d is defined, this can be deactivated through the user-defined configuration.

### 4.5 Verification

Given a list of probing sets  $\mathbf{P}^g$ , the verification step analyzes every  $\mathbf{P}^g_i \in \mathbf{P}^g$  by simulating intermediates recorded by the probes in  $\mathbf{P}^g_i$ . The same holds for  $\mathbf{P}^{g,t}$ . We give a high-level overview of the verification approach in Algorithm 6. By accomplishing the verification, the procedure returns a list encompassing the p-values  $p_i \in \mathcal{G}$  for each  $\mathbf{P}^g_i \in \mathbf{P}^g$ . The verification approach can be divided into three steps, presented as follows. Note that p-values refer to the result of statistical hypothesis tests explained in Section 2.4.

```

Algorithm 6 Verification of probing sets

\overline{\text{Input: }}(\mathbf{V},\mathbf{E})

▷ Circuit graph

Input: \mathbf{P}^g = \{\mathbf{P}_0^g, \dots, \mathbf{P}_{|\mathbf{P}^g|-1}^g\}

\triangleright List of probing sets (can be \mathbf{P}^{g,t} as well)

▶ Total number of simulations

Input: n_{\text{total}}

Input: n_{\text{step}}

▶ Number of simulations per step

Input: n_{\rm g}

▶ Number of groups

Output: \mathcal{G} = \{p_0, \dots, p_{|\mathbf{T}|-1}\}

\triangleright List of p-values

1: D ← ∅

▶ Initialize distribution tables

2: for i \in \{0, \dots, \frac{n_{total}}{n_{\text{step}}} - 1\} do

3:

\triangleright Initialize simulation results

\begin{array}{l} \mathbf{for} \ j \in \{0, \dots, \frac{n_{\text{step}}}{64} - 1\} \ \mathbf{do} \\ \text{Simulation}(n_{\text{g}}, \mathbf{V}, \mathbf{E}, \mathbf{S}_{j}) \end{array}

4:

5:

6:

UpdateDistributions(n_g, \mathbf{S}, \mathbf{P}^g, \mathbf{D})

7:

8:

\mathcal{G} \leftarrow \mathtt{Evaluation}(n_{\mathtt{g}}, \mathbf{D})

9: end for

```

#### 4.5.1 Simulation

The Simulation procedure in Line 5 of Algorithm 6 emulates the circuit for an arbitrary input sequence to compute all probed intermediates. Through the configuration (see Section 4.3), the user specifies the number of groups  $n_{\rm g}$  for which the statistical hypothesis test should be evaluated. Traditional tests in the context of SCA are either fixed versus random or fixed<sub>1</sub> versus fixed<sub>2</sub>, i.e., two groups. For each group, the user should naturally define the fixed value(s) or the random value (i.e., how many random bits are required). This should not be necessarily two groups, and PROLEAD supports any arbitrary number of groups, e.g., multiple fixed values.

The user further defines the maximum simulation length in number of clock cycles while the simulator emulates the circuit's state after each clock cycle iteratively. The user can also define an end condition to be checked during each simulated cycle. If the circuit state fulfills the end condition, the simulation terminates. A possible end condition is to stop if one or multiple primary outputs, e.g., a **done** signal, reached a specified value.

As given in Section 4.2.1, the given circuit is modeled as a Mealy machine consisting of a register stage storing the output of a combinational circuit, whose input is provided by a combination of the primary inputs and the registers' output. Therefore, once the masked primary inputs are prepared, the simulator starts iterating through the clock cycles. To this end, the following operations are performed per clock cycle until the end condition is met or the maximum number of clock cycles is reached.

- 1. The primary inputs are updated. More precisely, it is checked if for the current clock cycle a new value for the primary inputs is defined through the initial input sequence (see Section 4.3).

- 2. Register outputs are updated, i.e., the signals connected to registers' outputs reflect the corresponding values stored in the registers.

- 3. Now, the input of the combinational circuit is fully defined; hence, it can be evaluated. This is done following the concept of event-driven simulation. Since we consider no delay for the gates, this can be simplified by processing the combinational circuit in the order of the logical depth<sup>3</sup>. At the end of this step, the outputs of the combinational circuit (which are the circuit's primary outputs and/or the registers' input) are provided.

- 4. As the last step of every clock cycle, the registers store the values appearing at their inputs based on the status of their corresponding control signals, e.g., clock, enable, reset, etc.

Note that the above procedure is valid only for circuits, where all registers are synchronized, e.g., all of them see the positive-edge/negative-edge of the clock signal. PROLEAD optionally can handle other circuits, e.g., with latches and clock gating, but this requires to evaluate the combinational circuit two times per clock cycle, once when the clock signal is high and one more time when it is low (i.e., lower efficiency).

To decrease the runtime, the simulator of PROLEAD works on 64-bit variables, i.e., handling 64 independent simulations in parallel, which indeed follows the concept behind bit-slicing. We should highlight that only the above-given operations per clock cycle are performed on 64-bit variables. Almost all other operations, e.g., the group selection and preparation of masked primary inputs, are done ordinarily (not bit-sliced). Further, since simulations are fully independent of each other, several simulations are performed in parallel by means of multi-treading, which is also adjusted by the user though the configuration file. As shown in Algorithm 6, the total number of simulations is denoted by  $n_{\rm total}$  which is divided by  $n_{\rm step}$  (also defined by the user based on the available memory) denoting the size of each simulation set which should be performed before updating the evaluation results. This allows the user to observe the evaluation results after each  $n_{\rm step}$  simulations.

#### 4.5.2 Update Distributions

Before the evaluation takes place, we convert the simulation results into one individual and independent distribution table per probing set. This is essential since the statistical hypothesis test requires such distributions to estimate p-values. For this, we go through all simulations and concatenate the recorded bits of all  $p \in \mathbf{P}_i$  into a value with at least  $n_{\text{probe}}$  bits while  $n_{\text{probe}} = |\mathbf{P}_i|$ . In the following, we refer to these concatenated  $n_{\text{probe}}$ -bit values as keys. Each entry of a distribution table stores an individual key and how often the key occurs per group, i.e.,  $n_{\rm g}$  individual numbers.

For each set of  $n_{\text{step}}$  simulations, we compute the keys of each probing set and update the corresponding distribution table. To efficiently search for a key in the distribution table, we keep the distribution tables sorted by their keys. Hence, searching for keys has logarithmic complexity  $\mathcal{O}(\log n)$  in the number of observed keys. If a key is found in the table, the occurrence of the corresponding group is increased by one. Otherwise, an empty table entry with the new key (for all  $n_{\rm g}$  groups) is added into the sorted distribution table

<sup>&</sup>lt;sup>3</sup>Note that it should not be misunderstood that we do not cover glitches in our security evaluation. Indeed, we do not simulate the glitches, but the underlying glitch-extended probing model covers any form of glitches which may happen in the realization of the given circuit and affect its security.

before incrementing the corresponding occurrence. As we searched for the key before, the complexity for insertion into the sorted distribution table becomes independent of whether the key exists in the table or not. This process is also parallelized through multi-treading as the distribution table of different probing sets can be updated independently of each other. Hence, multiple distribution tables are updated in parallel and each table is modified only by a single thread.

#### 4.5.3 Leakage Evaluation

As given in Section 2.4, we make use of the G-test as the statistical hypothesis test. More precisely, we apply the G-test on the  $n_{\rm g}$  distribution tables of each probing set individually to achieve a measure for the independence of the distributions. Hence, we obtain the corresponding p-value  $p_i$  for each probing set, based on which we report the detectability of a leakage. This is the case if  $-\log_{10}(p)$  exceeds the predefined threshold, i.e., the null hypothesis  $H_0$  is rejected. Line 8 of Algorithm 6 performs this operations and stores p-values in  $\mathcal G$  which can be shown, printed, or stored in a file after each  $n_{\rm step}$  simulations.

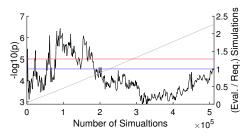

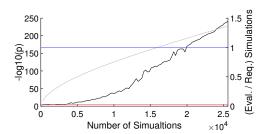

#### 4.6 Statistical Confidence

We refer to our results as statistically confident as soon as the error probabilities become acceptable. For the false positive probability, we predefine a threshold probability and reject  $H_0$  if the computed p-value becomes smaller than the threshold. As  $p < 10^{-5}$  is a common threshold for leakage assessment, e.g. t-test [SM15] and  $\chi^2$ -test [MRSS18], we decide to set the threshold probability to  $10^{-5}$ . Hence, the chance to falsely reject  $H_0$ , i.e. to report a secure design as insecure is smaller than  $10^{-5}$  for each probing set. However, false positives can become very likely if the number of probing sets exceeds  $10^{-5}$ . If this happens, e.g. if the experiment considers millions of probing sets, we recommend decreasing the threshold to an acceptable level. However, the decisive factor is not that the threshold is exceeded but that the p-value decreases continuously with an increasing number of simulations. To bring the false negative probability to an acceptable level, we apply the power analysis techniques introduced in Section 2.4. During the verification procedure, we continually monitor the sample size needed to satisfy statistical confidence for a predefined tuple  $(\beta, \varphi)$ . In particular, we numerically estimate the number of simulations required to satisfy an error probability of  $\beta$  for an effect size  $\varphi$ . To estimate the number of required simulations, we define a range in which we try to approximate the necessary number of simulations. In practice, we define a very large range from one to one billion to be sure that the number of required simulations lies in the range. Then, we apply a trial-and-improve strategy which is one-simulation accurate and achieves logarithmic complexity in the upper bound of the range. For the case studies in Section 5,  $\beta$  equals the threshold of  $10^{-5}$  for experiments with less than  $10^5$  probing sets while we set the effect size to  $\varphi = 0.1$ . Hence, by applying these parameters, we detect all small effects with an error rate of  $10^{-5}$ . While we suggest using these parameters as the default settings, we remark that the user can choose arbitrary parameters according to the desired security guarantees and the evaluated design. The estimation of required simulations takes place after each leakage evaluation step. As the computation of the statistical power depends on the degree of freedom, we estimate the number of required simulations for the probing set resulting in the highest degree of freedom. Hence, we can be sure that the estimated number of simulations is enough for all considered probing sets. Naturally, the degree of freedom grows with every new spotted intermediate that we store in the contingency table. Hence, the number of required simulations can only be estimated during the evaluation and grows if the degree of freedom grows. Nevertheless, the growth slows down or stops if all possible probed values of a set are considered in the contingency table. Hence, we stop the evaluation as soon as the number of performed simulations reaches the number of required simulations. In

Section 5.3, we visualize the progression of the different parameters based on two practical case studies in Figure 2.

### 5 Case Studies

In order to examine the ability as well as performance of PROLEAD, we evaluated several designs, which are mainly available through public repositories, like GitHub. In other cases, we either received the design from the corresponding authors or constructed the designs by ourselves. In short, PROLEAD can rapidly identify leakage in unmasked designs and those which we were aware of their security flaw. Further, we found out several mistakes and shortcoming of publicly-available masked designs which are supposed to be probing secure. In the following we elaborate each case study, but we keep the description of each one short and mainly refer to the original article.

**Setup.** We made use of Synopsis Design Compiler and NanGate 45 ASIC standard cell library to synthesis and generate the netlist of each case study. We made sure to avoid optimization across different modules (i.e., keeping the design hierarchy<sup>4</sup>) to not violate any assumptions of the original designer, e.g., not violating non-completeness [NRS11]. We further provided the functional description of most of the cells in the NanGate 45 library thereby PROLEAD can understand and simulate the given netlist (see Section 4.3). We ran the evaluations on a machine with an AMD EPYC 7352 (48 hyper-threading cores) and 128 GB of memory.

For the entire evaluations we considered two groups  $(n_g = 2)$ , one group fully random and the other one fully zero. In other words, we performed fixed versus random G-test when fixed inputs is  $\{0\}^t$  and random input  $\stackrel{\$}{\leftarrow} \mathbb{F}^t$ , where t stands for the size of the input vector. For all case studies, we kept the key of the design (if any) to the zero vector. Note that this does not have any effect on the result of our evaluations. However, if the design receives the key in a masked form, we gave the masked representation of the zero vector updated at the start of each circuit simulation.

For all case studies, we first conducted the evaluations by only covering glitches, i.e., no transitions. If we found no leakage, we then extended the evaluation by additionally covering the transitions. Therefore, if not stated, when we report vulnerability of a circuit, we mean when only glitches are taken into account. Likewise, when we report security of a circuit, we refer to the case where both glitches and transitions are covered. For all case studies, we set the effect size to  $\varphi=0.1$ . Therefore, if we report a design as secure, we mean that no effect with a effect size of  $\varphi\geq0.1$  was detected by PROLEAD. Only when we discover strong leakage, we increased  $\varphi$  to improve the readability of our results. The summary of all conduced evaluations are shown in Table 2.

#### 5.1 Unmasked Designs

The vulnerability of unmasked designs is expected. Hence, just for sanity check, we evaluated a round-based implementation of SKINNY-64 [BJK<sup>+</sup>16], which is available online<sup>5</sup>. PROLEAD reports first-order leakage at all clock cycles in less than a second using less than 100 simulations.

**Hiding Countermeasures.** When evaluating probing security of unmasked implementation, adding either amplitude or temporal noise does not have any effect on their vulnerability. Examples include adding an independent noise module, adding jitter to the

<sup>&</sup>lt;sup>4</sup>In Design Compiler this is achieved by setting -no\_autoungroup and -no\_boundary\_optimization switches for the compile\_ultra command.

<sup>&</sup>lt;sup>5</sup>https://sites.google.com/site/skinnycipher/downloads